In the world of system-on-chip (SoC) devices, architects encounter many choices when configuring processor subsystems. They range from single-processor cores to clusters to multi-core clusters that are mostly heterogeneous but occasionally homogeneous.

A recent trend is the widespread adoption of the RISC-V kernel based on the open standard RISC-V Instruction Set Architecture (ISA). The system is available under a royalty-free open source license.

In this regard, leveraging the plug-and-play capabilities of Network on Chip (NoC) technology has become an effective strategy to accelerate the integration of RISC-V based systems, an approach that facilitates seamless connectivity between processor cores or clusters and blocks of intellectual property (IP) from multiple vendors.

The basics of networking on chip

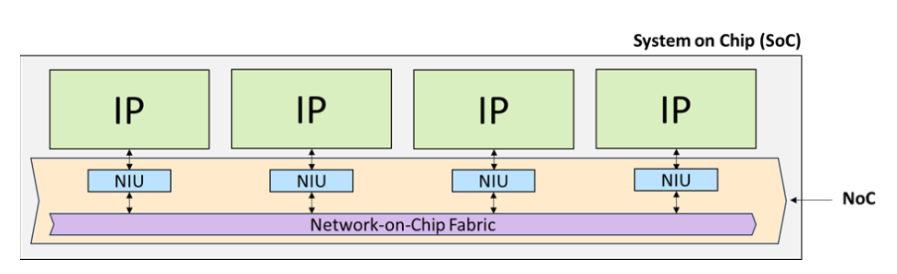

Interconnecting IP with NoC has several advantages. NoC can scale to the entire device, with each IP having one or more interfaces that span the entire SoC. These interfaces have their own data bandwidth, operate at different clock rates, and use a variety of protocols commonly used by SoC designers such as OCP, APB, AHB, AXI, STBus, and DTL. Each interface is connected to a corresponding network interface unit (NIU), also known as a socket.

NIU's role is to receive data from the transport IP and then organize and serialize this data into a standardized format suitable for network transmission. Multiple packets can be transmitted simultaneously. Upon reaching the destination, the associated socket performs the reverse operation, first deserializing and opening the data packet before submitting the data to the relevant IP. This process is done according to the protocol and interface specifications linked to that particular IP.

IP blocks can be visually represented as physical logical blocks. In addition, SOCs typically use a single NoC. Figure 1 shows a basic NoC configuration.

Figure 1: A very simple NoC representation showing the basic design configuration

NoC itself can be implemented using a variety of topologies, including 1D star, 1D ring, 1D tree, 2D network, 2D ring, and full network, as shown in Figure 2

Figure 2 The above example shows the various NoC topologies

Some SoC design teams may want to develop their own proprietary NoC, which is an extremely resource-intensive and time consuming process. Taking this approach requires teams of professional engineers to work for two years or more. To make things even more challenging, designers often spend as much time debugging and validating an in-house developed NoC as they do the rest of the entire design.

As design cycles shorten and revenue pressures increase, SoC development teams are looking at commercial NoC IP. This IP meets both the customization requirements required for an in-house developed NoC IP and can be obtained from a third-party vendor.

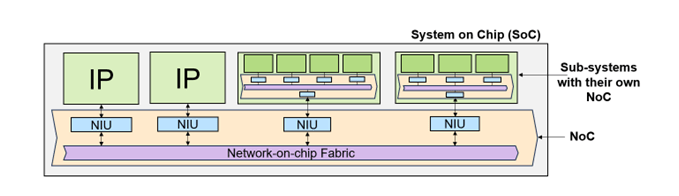

Another challenge to the growing complexity of SOCs is the use of multiple NOCs and various NoC topologies in a single device (Figure 3). For example, one part of the chip may adopt a hierarchical tree topology, while another part may choose a 2D mesh topology.

Figure 3 This diagram highlights subsystem blocks with internal NOCs

In many cases, the IP blocks in today's SOCs are equivalent to the entire SOCs of a few years ago, making them subsystems. As a result, the creators of these subsystem blocks often choose to adopt industry-standard NoC IP from third-party vendors.

In cases where a high degree of customization and co-optimization of computation and data transfer is required, such as processor clusters or neural network accelerators, the IP development team may choose to implement a custom transport mechanism. Or they may choose to use a less adopted, highly specialized protocol to achieve their design goals.

RISC-V and NoC integration

For standalone RISC-V processor cores, these ips provide an AXI interface for designers who do not need consistency and a CHI interface for designers who do. In this way, these cores can be plugged and played at the SoC level with the industry standard NoC.

Similarly, if the design team chooses a less commonly used inter-cluster communication protocol in the RISC-V design, the cluster can also have an ACE, AXI, or CHI interface for external connections. This approach enables a fast connection to the NoC of the SoC.

Figure 4 below shows the non-consistency and cache consistency options. In addition to their use in IP and SoC, these NOCs can also act as super NOCs (Super NOCs) in multi-chip systems.

Figure 4: NoC interconnect IP demonstrated in a multi-chip system

NoC IP in RISC-V processor

SoC designs for processor cores and clusters based on the open standard RISC-V instruction set architecture are increasing dramatically.

By leveraging the plug-and-play capabilities provided by NoC technology, the development and adoption of RISC-V based systems, including multi-chip systems, can be accelerated. This enables fast, seamless, and efficient connectivity between RISC-V processor cores or clusters and IP blocks from multiple vendors.

Heisener Electronic is a famous international One Stop Purchasing Service Provider of Electronic Components. Based on the concept of Customer-orientation and Innovation, a good process control system, professional management team, advanced inventory management technology, we can provide one-stop electronic component supporting services that Heisener is the preferred partner for all the enterprises and research institutions.