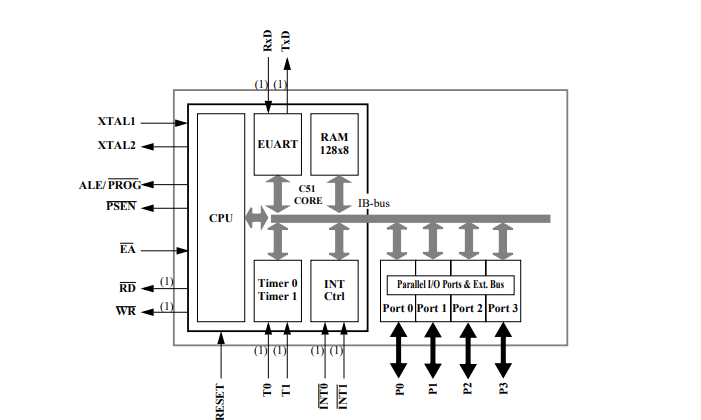

The TS80C31X2 is a high-performance CMOS and ROMless version of the 80C51 CMOS monolithic 8-bit microcontroller. The TS80C31X2 retains all the features of the TSC80C31, including 128 bytes of internal RAM, 5 source 4 priority interrupt system, on-chip oscillator and two timers/counters.

Block diagram

In addition, the TS80C31X2 features dual data Pointers, more general serial channels for easy multiprocessor communication (EUART) and X2 speed improvement mechanisms. The TS80C31X2's all-static design allows for reduced system power consumption by reducing the clock frequency to any value (even DC) without loss of data.

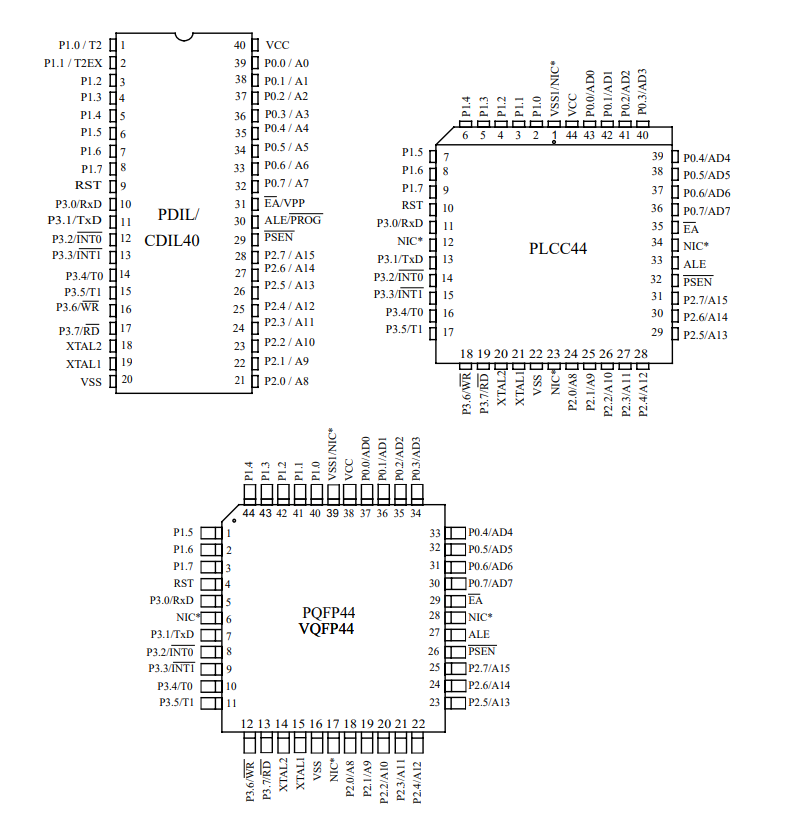

Pin Configuration

The TS80C31X2 has 2 software selectable reduction activity modes to further reduce power consumption. In idle mode, the CPU is frozen while the timer, serial port, and interrupt systems are still running. In power-off mode, RAM is saved and all other functions are disabled.

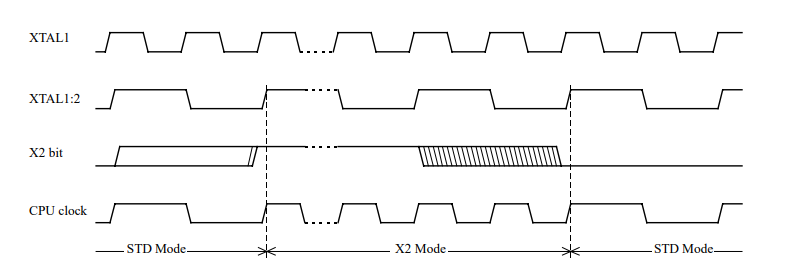

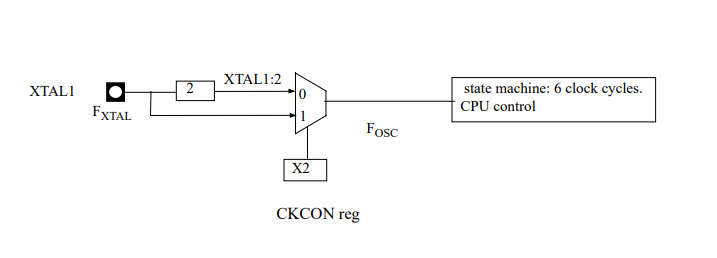

The clock of the entire circuit and peripherals is divided into two parts before being used by the CPU core and peripherals. This allows any cycle ratio to be accepted on the XTAL1 input. In X2 mode, since this divider is bypassed, the signal on XTAL1 must have a cycle ratio between 40 and 60%. Figure 1. Clock generation block diagram is displayed. The X2 bit is verified on the rising edge of XTAL1÷2 to avoid failure when switching from X2 to STD mode. Figure 2. Display mode switching waveform.

Clock generation graph

Mode switching waveform